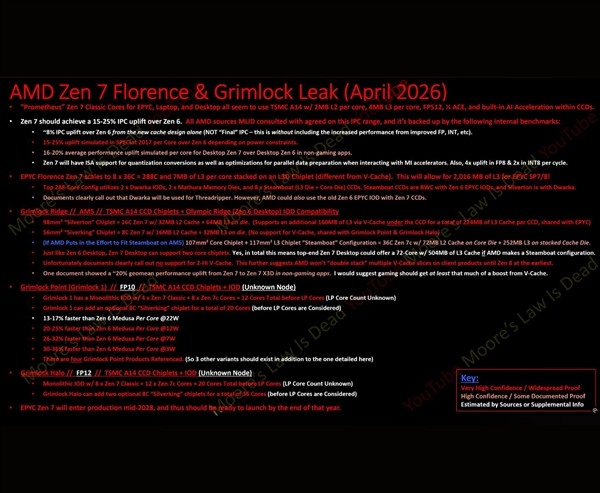

Florence採用兩顆Dwarka I/O晶片和兩顆Mathura記憶體晶片,均基於TSMC N3C工藝。

每個Steamboat CCD由一顆台積電A14節點的Zen 7核心晶片,與一顆N4P節點的L3快取晶片堆疊而成,與現有3D V-Cache不同的是,快取晶片堆疊在核心晶片下方而非上方。

每核配備7MB L3快取,支援PCIe 6.0和CXL 3.2介面,xGMI4-80G互連速度,TDP最高600W。

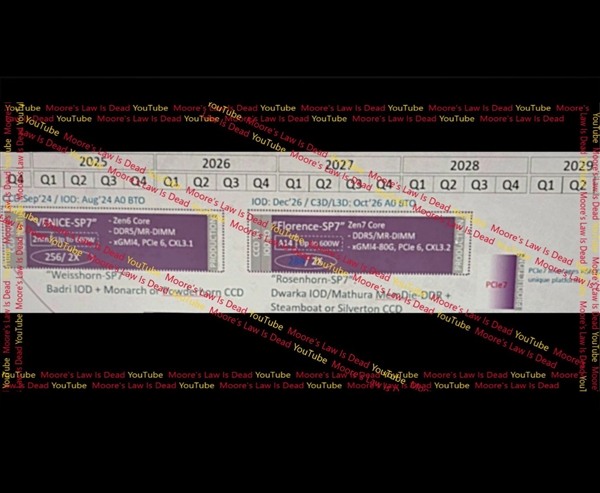

時間線上,A0流片計畫於2026年10月,量產目標為2028年中,正式發佈預計在2028年底。

此外,路線圖中還出現了PCIe Gen 7平台,預計2029年到來,可能作為新一代介面的半代更新。

對使用者而言,一個關鍵資訊是相容性,洩露文件顯示Zen 7 CCD可相容上一代Kedar和Weisshorn I/O晶片,Silverton CCD則支援Badri、Kedar、Puri和Dwarka IOD,覆蓋SP7和SP8封裝,支援每插槽2/4/6/8顆CCD。

針對消費市場的Silverton和Silverking 的洩露性能資料顯示,在低於9W的伺服器工作負載下,Zen 7每核性能提升16%-20%;而在3W/核的客戶端APU場景下,能效提升達到30%-36%。

MLID推測,36核Steamboat CCD的尺寸與16核Silverton相近,理論上AMD可以在AM5封裝上塞入兩顆Steamboat,實現72核桌面處理器。

不過洩露幻燈片中並未確認此類產品,MLID本人也認為這類晶片更可能面向嵌入式市場而非DIY玩家。

說到底還是雙通道頻寬不夠用

說到底還是雙通道頻寬不夠用