moacetyl wrote:

devine...(恕刪)

2025-07-17 14:45

記者署名:

記者高兆麟/台北報導

原文內容:

晶圓代工龍頭台積電(2330)今(17)日舉行法說會,並公佈 2025 年第2季財務報告,稅後純益 3982 億 元,每股盈餘 15.36 元,創下史上單季新高,台積電ADR美股夜盤反應業績利多飆漲逾6%。

台積電ADR連續2個交易日收盤、盤中同步創下史上新高,美股16日以上漲0.61美元或0.26%、237.56美元作收。

台積電在台股今日收盤後公布第2季財報,數據亮眼,除單季獲利創下史上單季新高外,單季毛利率攀升至58.6%,均大幅超越市場預期,也帶動台積電ADR美股夜盤股價,股價直拉走揚,最高上漲15美元至252.99美元,大漲6.5%。

https://finance.ettoday.net/news/2998027

照魏先生的說法,未來五到十年會"非常好"~~

照魏先生的說法,未來五到十年會"非常好"~~

台積電:十年內生意非常好 董座魏哲家憂心關稅讓全世界經濟往下掉

eriks626 wrote:

2030年連中國應該...(恕刪)

半導體這行有Road Map

畢竟台積電也只是個工廠

設備與材料都要靠供應商

所以上下游的整合都有時間表

不過在製程整合/良率這一塊

到了2030

還是獨霸...

------------------------------

「美國的AI Infrastructure發展以及先進封裝的重要性」

最近,在美國舉行了一場”Winning the AI Race”的event,美國的創投專家、政府官員、和科技業的大老們聚在一起,討論美國要如何贏下這場AI的競賽。

NVIDIA執行長Jensen Huang、AMD執行長Lisa Su、Y Combinator的Partner Paul Buchheit……等人都齊聚一堂討論未來的策略。

美國正在嘗試以國家的角度來整合資源,並集結投資界和業界的資源、Insights及努力,希望能在AI的競賽中取得主導地位。

而這就連結到新一波的AI Infrastructure建設,如OpenAI Sam Altman & Softbank孫正義共同宣布的Stargate計畫。

看起來美國開啟了新一波對AI的發展計畫。不過,這一篇就讓我們以AI發展和半導體的角度,來討論一下AI Infrastructure的發展,以及其中關鍵的半導體技術:先進封裝。

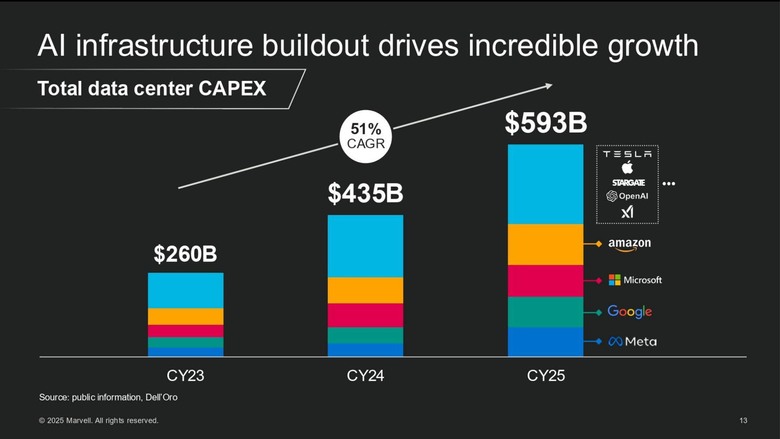

▌2030年的AI Infrastructure計畫

從目前各大巨頭對AI的計畫我們可以發現,現在整個AI Infrastructure的發展並沒有要慢下來的意思。

相反的,目前Big Tech、OpenAI、xAI…..等公司之間的競爭,反而讓這樣子的發展持續高速進行。

目前主要用來訓練新模型的GPU數量,大多都在10萬顆GPU的這個層級。

以目前Stargate公布在Abilene (Texas)還有與Oracle加碼的計畫看起來,未來幾年會很快的到達200萬顆GPU的層級。而xAI、 Meta也有計劃要建構百萬以上GPU的Data Center。

因此,到2030年之前,我們將會看到很多百萬顆GPU以上的Data Center出現。

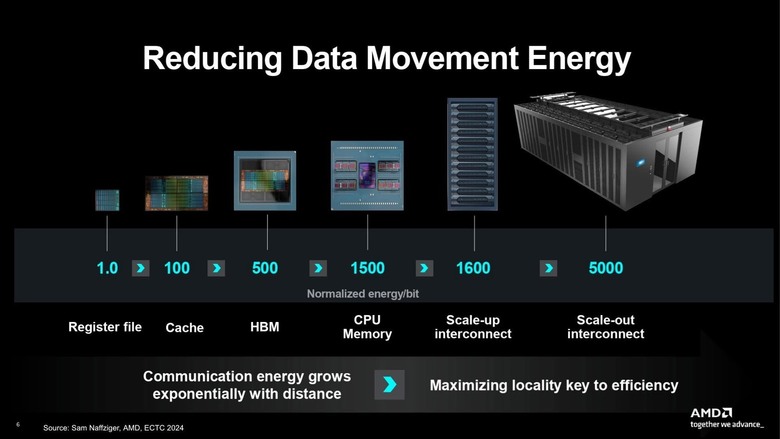

不過,接下來的挑戰在於,以Data Center中晶片互連的數量指數增加的情況來看,晶片和晶片互連的效率會未來一個很重要的關鍵。

▌半導體硬體的挑戰:晶片和晶片互連的效率

現在看起來,目前業界的作法會是持續的計畫更大型,更多資料中心。然後再在晶片的硬體上進行優化。

傳統的作法會是在製程節點上升級,而這樣的升級會帶來電晶體密度的增加以及能耗效率的提升。

不過,一是製程節點上面的升級已經不足以滿足需求,二是晶片間資料的傳輸在Data Center晶片數量增加下會有更大的能耗。

因此,需要更好的方法降低晶片和晶片之間資料傳輸的能耗。

而目前看起來先進封裝會是非常關鍵的技術。

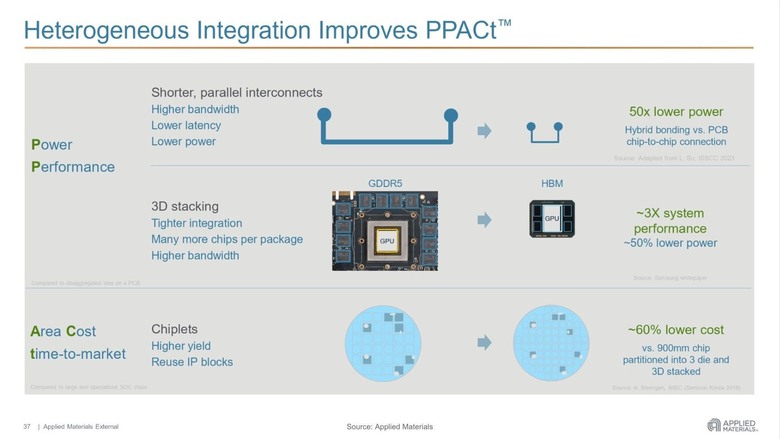

▌解決方案:先進封裝的重要性

一般來說,大家會將焦點放在晶片和晶片互連的技術上,比如說Silicon Photonics,將電訊號傳輸轉成光訊號傳輸就是一個好的方式。

不過,我們現在會看到更多先進封裝的技術被用來降低整體系統的能耗。

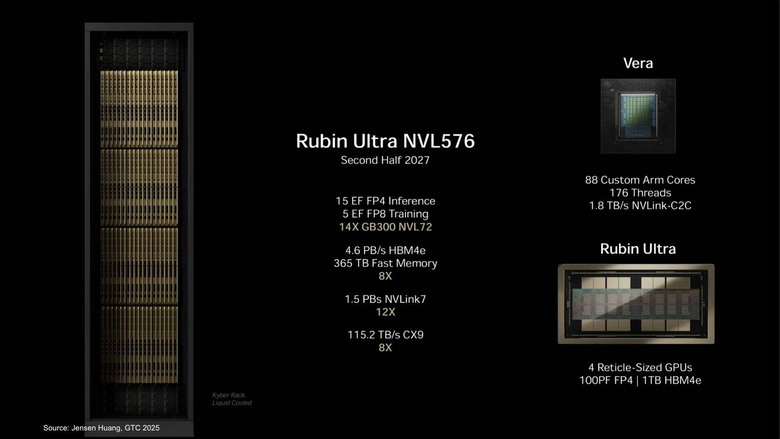

首先,我們看到更大的2.5D封裝被用來取代更多的晶片互連,比如說原本NVIDIA NVL72是讓72顆GPU互連,每顆GPU為2倍的Reticle Size (就是把2顆GPU封裝在一起),但是,接下來在2027年會發佈的Rubin Ultra NVL576,就會是4倍的Reticle Size的Rubin Ultra (就是把4顆GPU封裝在一起),然後把144顆Rubin Ultra串連在一起。

原本更大GPU cluster的一部分串連,用更大的2.5D封裝來取代。

另外,像用先進封裝和Silicon Photonics整合的Co-Packaged Optics (CPO),接下來會被各家公司使用在Switch晶片上,或是和XPU的互連。都充分的顯示先進封裝的意義不只是在單純封裝上,也是大幅增加晶片和晶片互連效率的重要技術。

▌先進封裝的產能需求:先進封裝為目前半導體產業的發展關鍵

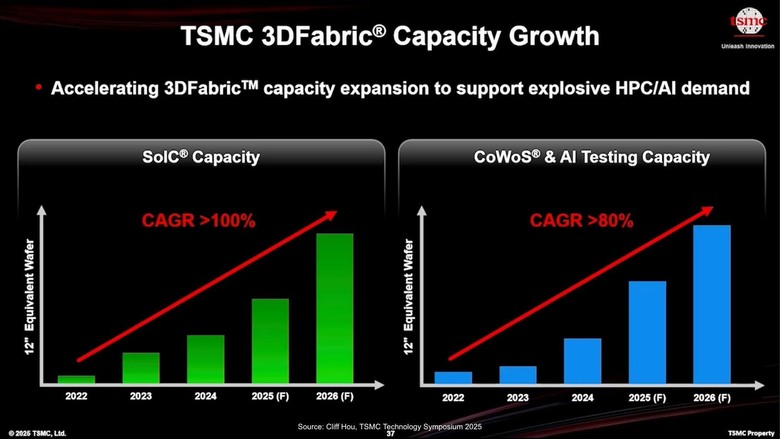

因此,我們從TSMC的計畫來看,我們會發現過去這幾年先進封裝的產能增加速度,2.5D封裝的CoWoS是80%以上的年增長率,而3D封裝的SoIC,則是更誇張的以100%的年增長率在增加。

相比於先進製程不到50%的產能增加速度,可以發現先進封裝會是目前AI Infrastructure硬體發展的重點。

而從2.5D封裝和3D封裝發展的Roadmap來看,我們可以發現2.5D封裝的尺寸還在快速的變大,這顯示了未來晶片互連會積極的使用先進封裝來幫助優化。

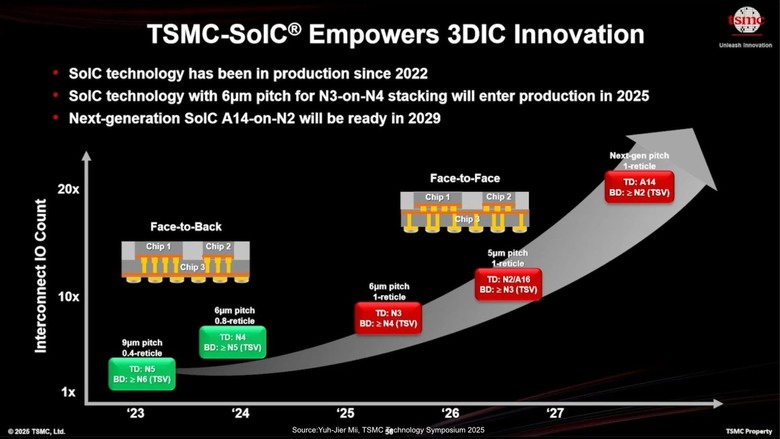

而3D封裝則是將IO pitch尺寸微縮,讓晶片能夠以更低的能耗來傳輸更大量的資料。

關閉廣告