https://hothardware.com/news/analyst-reports-apples-m3-tape-out-cost-1-billion

蘋果全新的 M3 處理器即將推出,以補充其 M2 前代處理器,根據半導體分析師 Jay Goldberg 的說法,新晶片的流片花費了頻果的一大筆錢。事實上,將三款 M3 晶片投入製造階段的總成本可能已達到約 10 億美元。如果這是真的,這意味著蘋果需要銷售相當多的 M3 驅動的 Mac 電腦才能收回任何實際資金。

該報告來自Jay Goldberg 經營的Digits to Dollars 博客 (https://digitstodollars.com/2023/11/02/apple-m3-and-the-state-of-cpus/),其中大部分內容關注 M3 系列的經濟效益。他估計整個 M3 系列的流片成本為 10 億美元,這指的是設計處理器和準備製造的所有工作。戈德伯格指出,儘管這些處理器僅出現在蘋果產品中,但該公司在研發方面的支出與英特爾或高通相當(甚至超過)是合理的,因為蘋果的利潤率要高得多。

然而 10 億美元並不算總預算。首先,台積電 3nm 節點的製造成本非常昂貴,並且肯定會削減蘋果新晶片的利潤,就像任何尖端節點的情況一樣。然而,如果台積電 3nm 製程良率低的傳言屬實,生產成本可能會比平常更高。低良率是高缺陷率的結果,這導致矽的使用效率較低。此外,較大的 CPU(例如 M3 Max)的良率較低,特別是在缺陷率相對較高的情況下。

目前還不清楚Digits to Dollars引用的 10 億美元數字是否 假設蘋果只需要一次流片。如果效能意外不佳或遇到某種錯誤(或勘誤表),許多 CPU 都需要新的步進或版本。雖然許多現代處理器已成功推出 A0 晶片(這實際上是第一個流片),例如 RX 7900 XTX/XT,但有時效果並不總是那麼好。小修改(如 A1 或 A2)不會那麼昂貴,但大修改(B0 或 C0)會花費更多。

無論具體細節是什麼,很明顯蘋果在其最新處理器上花費了大量資金,該公司無疑希望其下一代 Mac 筆記型電腦和桌上型電腦能夠彌補這一點。

蘋果前兩代就已經把MAX用UltraFusion(基於TSMC CoWoS-S的再設計,蘋果有專利號) 互聯後倍增規模再以Ultra型號發佈,他們打從第一代起就在用小晶片設計了

eclair_lave 忘了 [點點點]

個人積分:5506分

文章編號:88555699

eclair_lave 有時候覺得部分安卓廠用的料件都是上一兩代技術 然後賣跟哀鳳差不多價 真的很噁心 技術力製造工藝都跟不上 還敢開那個定價

skiiks 哀鳳有些地方也是很噁心,CPU用上最頂尖的設計,周邊的支援卻鎖東鎖西,type-c的充電功率依然保守,喊了好幾年才開放typec。

流個片就有10億鎂?

以後幫客戶流片就好,單季流個20片Intel一輩子都別想追上?

出處台積電代工價碼、研發成本

piefucker wrote:

也沒講10億美元成本是根據那裡來的資訊,

這分析師是什麼分析師?網站分析師?

"分析"師 比較好聽啊,感覺就很權威讓你不能嘴,

腦補師多難聽...

自律努力讓自己變大隻

英文標題直接中翻的誤會,其實那篇報導看內容講的是指這三款SOC直到流片的總支出

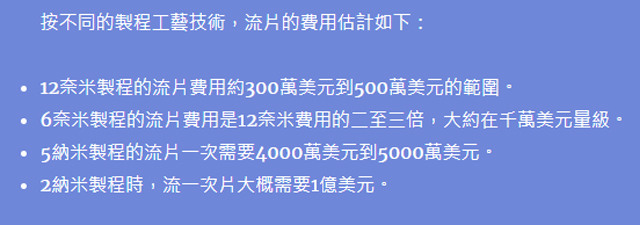

單指流片的話,5nm流片一次約4~5千萬鎂,3nm好像沒看到有參考資料

loki6865 wrote:

製程開發費跟廠商流片費原來是同一碼事? 這種花邊消息瞎引用多的去,(14900K上市前什麼6.4GHz、32C滿街跑)光是原文就一堆可能、若是的字眼...還分析咧

就跟7樓講的一樣,看不出該位分析師是拿到台積電實際報價單數據分析,或是待過台積電還是合作過怎樣...甚麼都沒有?

==

也許該分析師用詞不精確 (應該是含設計費用?)

根據 https://min.news/en/tech/def29226dea2b06f47efea4aae13e8f3.html

國際商業策略公司(IBS)執行長Handel Jones表示:「設計一顆28奈米晶片的平均成本為4000萬美元。相較之下,設計一顆7奈米晶片的成本為2.17億美元,設計一顆5奈米晶片的成本裝置成本為4.16億美元,3nm設計成本將高達5.9億美元。”

在先進製程設計成本方面,知名半導體技術研究機構Semiengineering也計算了不同製程下晶片的成本。其中,28nm節點上的晶片開發只需要5,130萬美元,16nm節點需要1億美元,7nm節點需要2.97億美元。到5nm節點,開發晶片的成本將達到5.42億美元。3nm節點的資料目前還沒有,可能是因為3nm還處於開發階段,成本不好估計。但從這個趨勢來看,3nm晶片研發費用可能會接近10億美元。

畢竟光是一次流片就至少要3個月+,如果沒能一次搞定還要修正後再跑一次,還不提流片後的驗證過程,跟流片前的設計工程,這些工作一年內做不完

舉個參考例子,預計明年面市得ZEN5,從資訊看研發專案起始是2018,再往前完整跨代架構得產品,從無到有耗時也約4~5年左右,當然不是每一種CPU/SOC都開發週期要這麼長就是,還是要看複雜度而定

小惡魔新聞台

小惡魔市集

為提供您更優質的服務,本網站使用cookies。若您繼續瀏覽網頁,即表示您同意我們的cookies政策。 了解隱私權條款