Intel Tiger Lake 處理器。

Intel 在昨晚舉行 2020 年 Intel 架構日的線上發表,揭露了新一代 Willow Cove 微架構、Tiger Lake 處理器以及 Xe 顯示晶片架構的相關消息,並且宣佈將會以新一代 10 奈米製程的 SuperFin 電晶體技術,提供效能更好、耗電量更低的處理器表現。

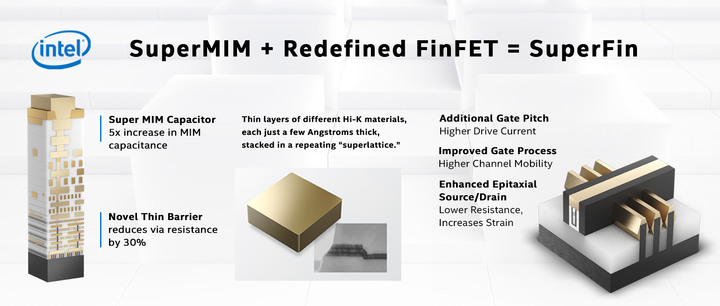

SuperFin 電晶體技術

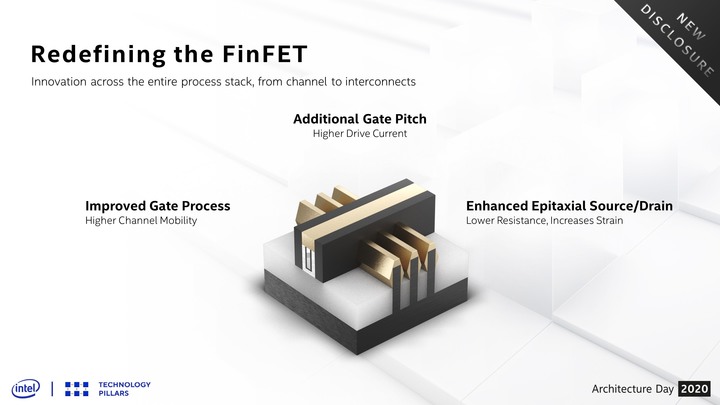

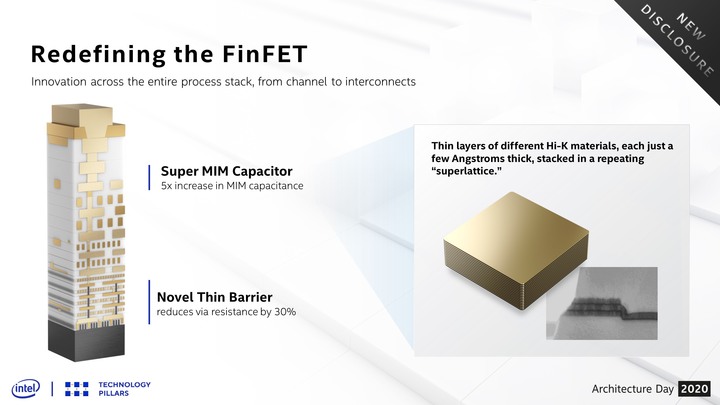

SuperFin 電晶體技術主要是 Intel 將增強型 FinFET 電晶體與 Super MIM 電容器進行結合,透過改善柵極製程以及提供額外柵極間距的選項,讓更多電流以更快的速度通過通道來提高效能。另外 Intel 也透過新型薄阻障層,將通孔電阻降 30%,增加互連效能。另外 Intel 這次也透過新型的 HI-K 介電材料,在 SuperMIM 電容部分提供 5 倍的容值,減少運作時的電壓驟降狀況,進而提高產品效能。

SuperFin 改良後的柵極設計。

Super MIM 電容器。

Intel SuperFin 的介紹影片:

SuperFin 將首先運用在 9 月份發表的 Tiger Lake 處理器上,Intel 並且表示目前已經開始生產並且出貨給 OEM廠商,預計將在年底推出搭載TigerLake 處理器的機型。

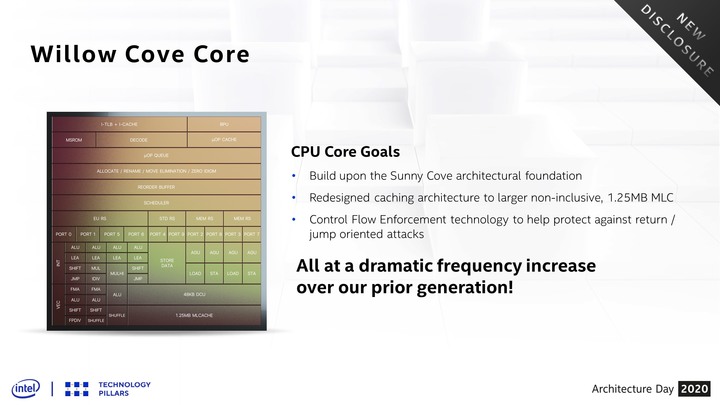

Willow Cove 微架構

Willow Cove 微架構。

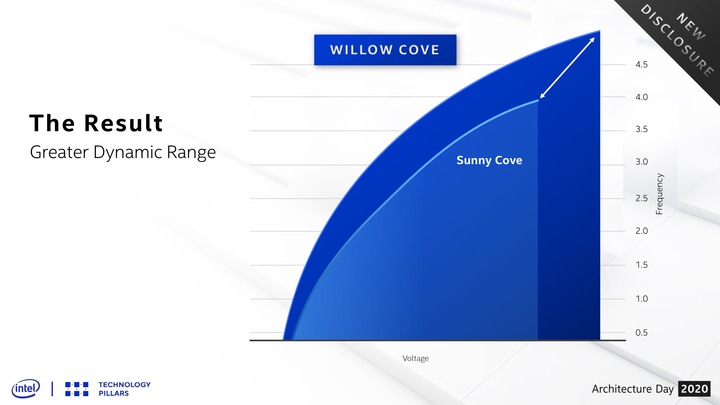

除了 SuperFin 技術外,這次 Intel 也在架構日上提到新一代 Willow Cove 微架構的消息,主要是在原有 Sunny Cove 的基礎上,導入上述 SuperFin 電晶體技術,讓 Willow Cove 微架構在頻率/電壓比上,比 Sunny Cove 有更大的操作彈性,在同樣電壓設定下,Willow Cove 能提供更高的時脈表現,Intel 表示 Willow Cove 在動態時脈的提升幅度甚至超越一個世代。

Willow Cove 在電壓/時脈的操作彈性。

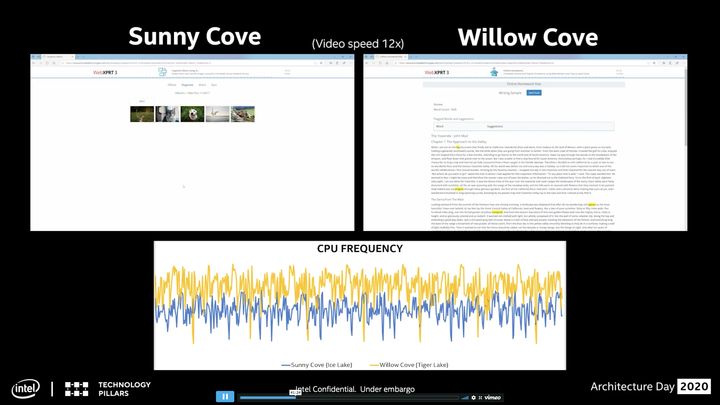

在 WebXPRT3 網頁效能測試時,採用 Willow Cove 的 Tiger Lake 處理器(黃色) 與 與採用 Sunny Cove 的 Ice Lake 處理器(藍)在時脈上的差異。

另外在外部快取架構部分,Willow Cove 在重新設計後,能夠支援更大的 1.25MB L2快取,並透過 Intel 控制流強制技術(Intel Control-flow Enforcement Technology)來防護返回/面向跳轉攻擊。

Tiger Lake 處理器

Intel Tiger Lake 處理器。

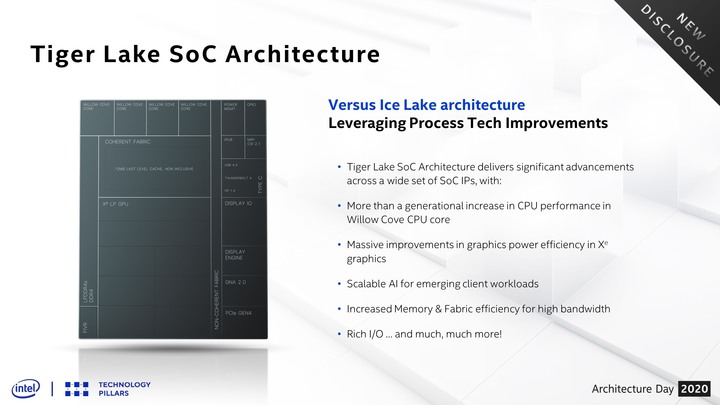

在即將於 9 月份推出的 TigerLake 處理器部分,則是導入 Willow Cove 微架構與 SuperFin 電晶體技術,並且加入了 Xe-LP 顯示核心,提高處理器在 AI 與顯示上的面的效能,並且整合了 Thunderbolt 4 技術,以下是 Tiger Lake 的重點特色:

- 全新 Willow Cove CPU 核心 – 利用 10 奈米 SuperFin 技術提升頻率表現。

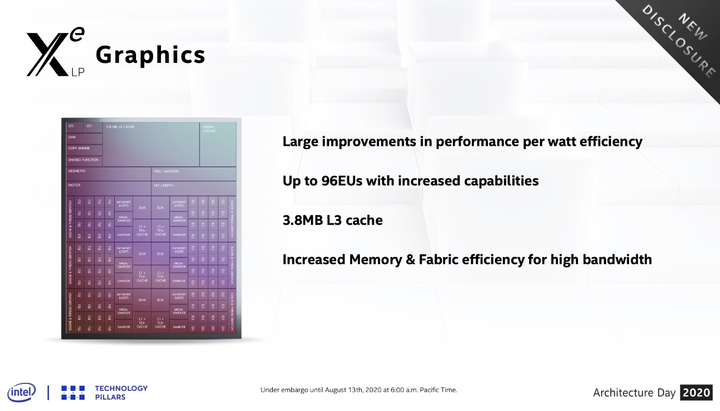

- 最多達 96 個 EU(執行單元)的新型 Xe 繪圖,提升每瓦效率。

- 電源管理 – 一致性結構中的自律 DVFS,提高 FIVR 效率。

- 架構和記憶體 – 一致性結構頻寬增加 2 倍,記憶體頻寬提高到 86 GB/s,架構相容 LP4x-4267、DDR4-3200;LP5-5400。

- 記憶體採用專用結構通道。

- GNA 2.0 專用 IP,可從 CPU 卸載並進行低功耗神經網路推論,與單純使用 CPU 相比,使用 GNA 的 CPU 使用率降低約 20%(噪音抑制工作負載)。

- 整合 Thunderbolt 4 / USB4、PCIe Gen 4 介面。

- 顯示同步頻寬最高達 64 GB/s。

- 支援 6 個 4K30p 視訊串流、最高提供 4K90p 和 4 千 2 百萬畫素影像架構相容能力。

Tiger Lake 將採用的 Xe LP 顯示核心。

Intel TigerLake 處理器的官方影片:

Alder Lake 處理器

Alder Lake 將會承繼 LakeField,在 2021 年推出混合式架構處理器。

這次 Intel 也揭露了次世代 Alder Lake 混合式架構的消息,將採用 Willow Cove 下一代的 Golden Cove(大核)與 Gracemont(小核)組成大小核搭配,將在 2021 年登場,不過詳細的規格與效能數字並未透露。

(這技術目前是以10nm製程為基礎打造的)

(這技術目前是以10nm製程為基礎打造的)

)

)