在新任執行長 Pat Gelsinger 上任之後,Intel 對於自家新技術的對外宣示動作不斷,在上半年宣佈了 IDM 2.0 之後,在今天(7 月 27 日)的『Intel Accelerated』活動中,再度大動作的揭露了到 2025 年 Intel 的製程技術藍圖,發表了全新的 RibbonFET 電晶體架構以及 PowerVia 背部供電設計,並且一改過去以閘極長度為準的製程命名策略,企圖扭轉市場上 Intel 製程落後的印象。

Intel 在今天的 『Intel Accelerated』活動中,公佈了未來的製程發展計畫。

推翻過去的節點命名策略

Intel 今天宣布了新的製程節點命名策略。

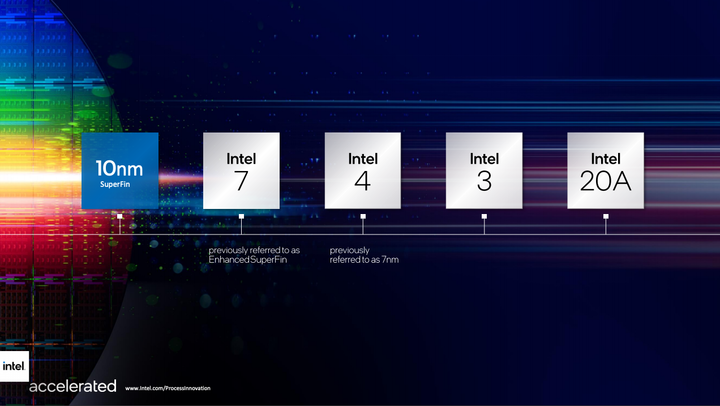

這次在『Intel Accelerated』活動中,受到最大關注的製程節點重新命名策略,過去 Intel 是以閘極長度為準作為命名方式,但隨著半導體製程技術的進步與分歧,Intel 認為這種命名策略很容易讓客戶誤解,而推出了全新的製程節點命名方式,未來將以 『Intel 7』、『Intel 4』、『Intel 3』 以及『Intel 20A』等作為新製程節點的名稱,今天也針對新名稱所代表的技術提出說明

Intel 以單一數字對應目前的奈米等級製程(Intel 7、4、3)以及未來的埃米等級製程( Intel 20A)。

目前的 10nm SuperFin 產品,已經在奧勒岡、亞利桑那與以色列的工廠進行大量生產。

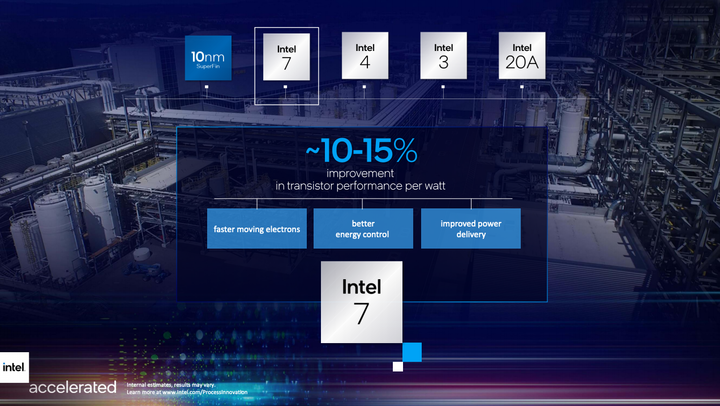

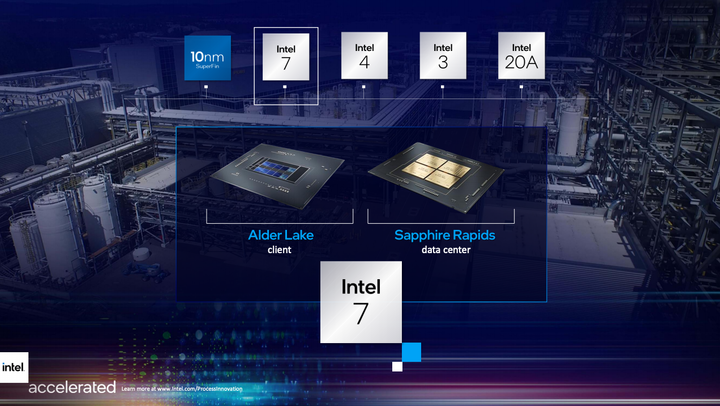

Intel 7:對應先前的 10nm+ 製程階段,針對現有的 FinFET(鰭式場效電晶體)進行最佳化配置,相較現行的 10nm SuperFin 製程,每瓦效能可提升大約 10%~15%。預計在今年下半年的 Alder Lake 處理器以及 2022 年第一季量產的 Sapphire Rapids 資料中心處理器將會使用這個製程。

Intel 7 製程的特色。

運用 Intel 7 製程的產品,包括 Alder Lake 處理器以及資料中心運用的 Sapphire Rapids 處理器。

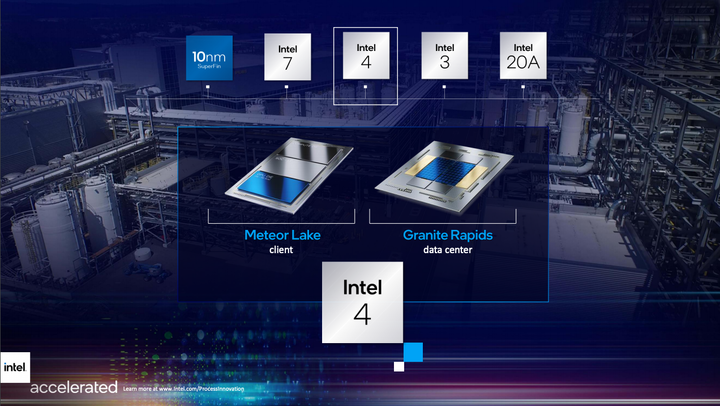

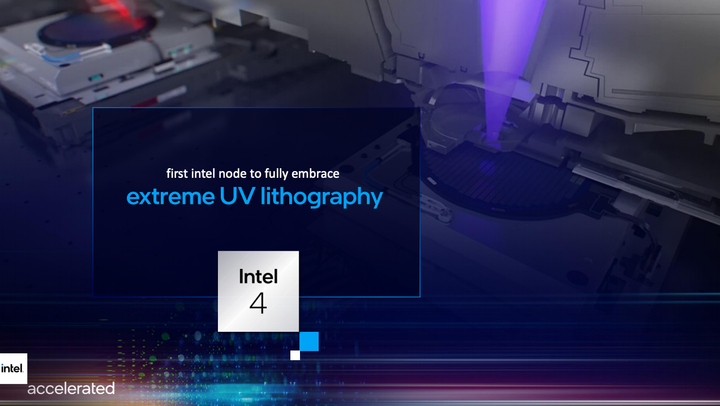

Intel 4:對應先前的 7nm 製程,全面使用極紫外光(EUV)微影技術,每瓦效能提升約 20% 並且縮小晶片面積。Intel 4 預計將在 2022 下半年準備量產,2023 年開始出貨,首先出貨的產品將會是代號為 Meteor Lake 的處理器以及 Granite Rapids 資料中心處理器。

運用 Intel 4 製程的產品,為 Meteor Lake 處理器以及 Granite Rapids 資料中心處理器。

Intel 4 也將是首個 Intel 運用 EUV 極紫外光微影技術的製程節點。

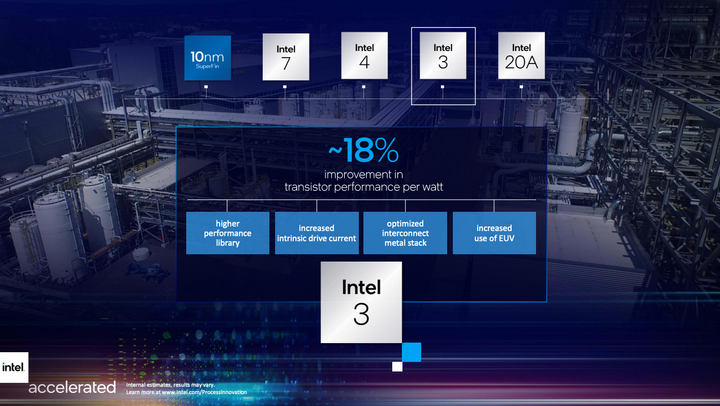

Intel 3:則是針對 Intel 4 製程作出改進設計,提升 FinFET 技術效能以及提升 EUV 的使用比例,目標是較 Intel 4 在每瓦效能提高 18%,並且再進一步縮小晶片面積。Intel 3 製程將於 2023 下半年準備開始生產。

Intel 3 製程節點技術的特色。

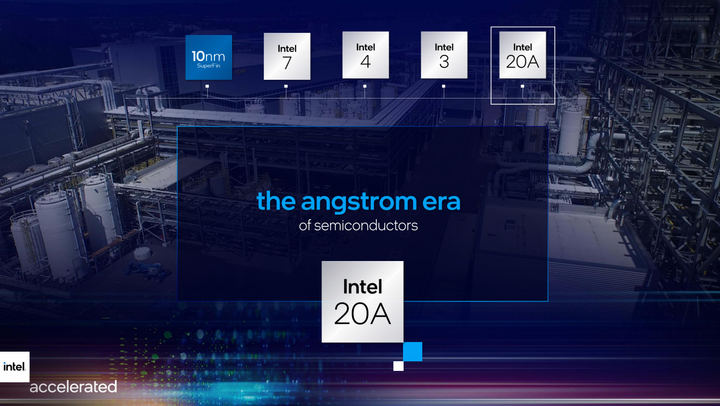

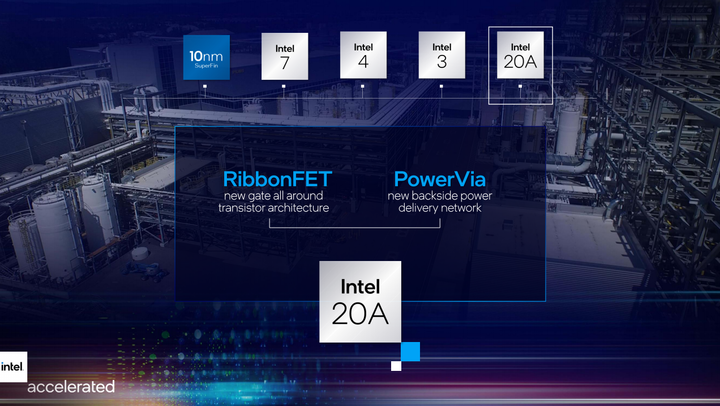

Intel 20A:而這次 Intel 也首度公佈了埃米(angstrom,0.1 奈米)等級的 Intel 20A 製程(其實就是 2nm,感覺有點.....),並且宣布將在這個製程中首度運用新的電晶體結構以及背部供電技術,來提高電晶體的性能表現。Intel 宣布 20A 製程預計於 2024 年逐步量產,而且已經有客戶:高通 Qualcomm 將採用 Intel 20A 製程技術來製造其產品。

Intel 宣布以 20A 技術進入埃米(10 的負 10 次方)世代。

新的電晶體架構:RibbonFET 以及背面供電設計:PowerVia

Intel 20A 製程中的兩大新設計:RibbonFET 架構與 PowerVia 背部供電技術。

而這次 Intel 也公布了新電晶體架構:RibbonFET,是 Intel 預計將在 2024 年登場的『Intel 20A』製程節點中所運用的新技術。。RibbonFET 是 Intel 採用環繞式閘極(Gate All Around)電晶體設計的實作成果,也是 Intel 在 2011 年推出 FinFET 設計後的首次全新電晶體架構。RibbonFET 的特色是在較小的面積當中堆疊多個鰭片,於相同的驅動電流提供更快的電晶體開關速度。

Intel RibbonFET 電晶體架構。

另外 Intel 也推出了 PowerVia 背部供電技術,採用業界獨特的晶圓背面供電設計,以移除晶圓正面供電所需迴路,來減少正面供電對於電晶體訊號傳遞的干擾,對單一電晶體的效能做出最佳化。

傳統正面供電設計(左)與 PowerVia 背部供電設計(右)的差異。

RibbonFET 電晶體架構與 PowerVia 背面供電設計介紹影片:

再度強調封裝架構的創新

Intel 在封裝技術上的演進。

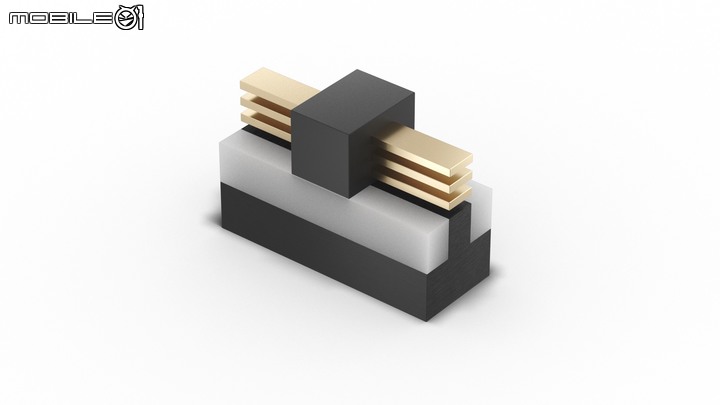

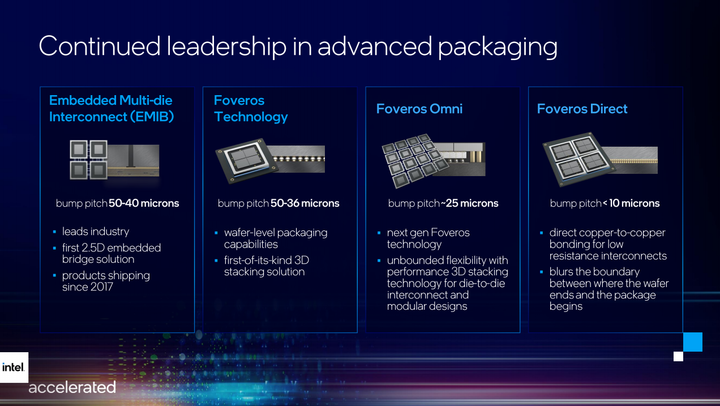

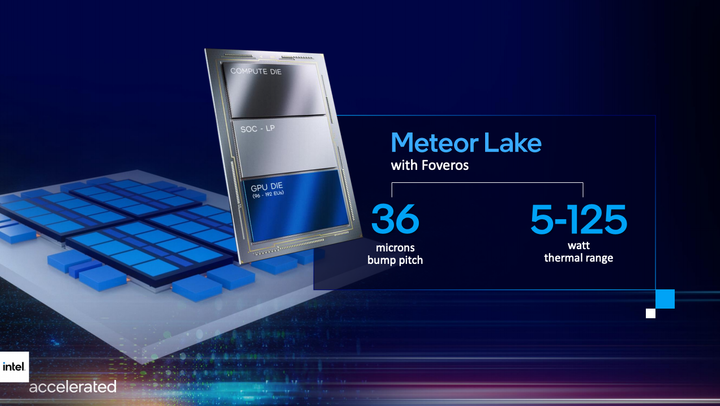

除了更新製程節點以及新電晶體架構外,Intel 在這次活動中也再度強調的自家 3D 封裝技術的創新,除了在現有的 2.5D EMIB (embedded multi-die interconnect bridge)嵌入式橋接解決方案持續改良,將凸點間距(bump pitch)由 55 微米降低至 45 微米外,在 Foveros 3D 堆疊解決方案上則是宣佈將會運用在 Meteor Lake 處理器上,凸點間距降低至 36 微米,TDP 則為 5 至 125W。

Meteor Lake 處理器將採用 Foveros 封裝技術。

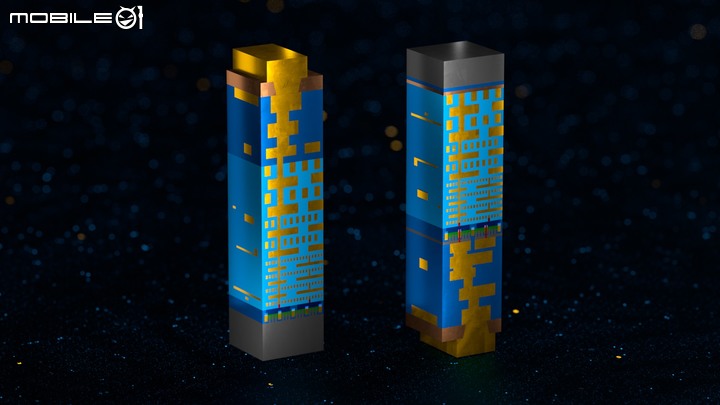

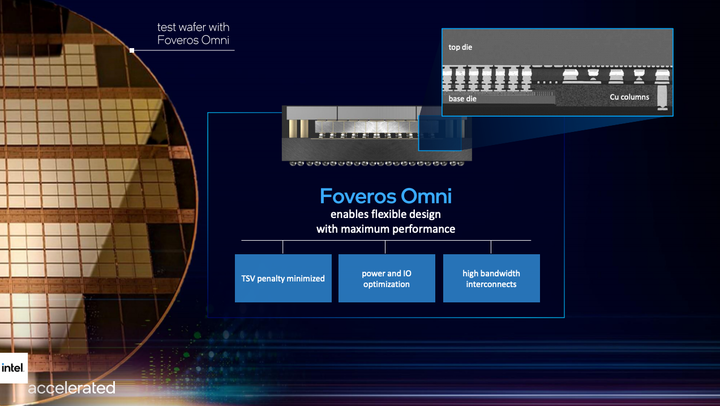

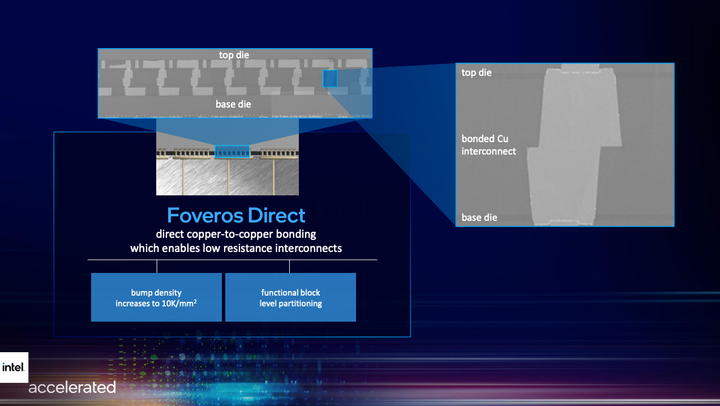

另外在新款封裝技術部分,Intel 這次則是持續更新 Foveros 3D 堆疊解決方案,公佈了採用晶片與晶片連結與模組化設計、可混合多種不同節點、分拆晶片設計的 Foveros Omni 封裝技術。以及採用直接銅對銅接合技術,讓凸點間距降低至 10 微米以下的 Foveros Direct,兩者都預計將在 2023 年登場。

Foveros Omni 封裝技術。

Foveros Direct 技術。